# Fast and Furious Quick Innovation from Idea to Real Prototype

Simone Fontanesi, Infineon Technologies Austria AG, Villach, Austria Gaetano Formato, Infineon Technologies Austria AG, Villach, Austria Thomas Arndt, COSEDA Technologies GmbH, Dresden, Germany Andrea Monterastelli, Infineon Technologies Austria AG, Villach, Austria

1 Motivation

2 Methodology

Results and Conclusions

## Selling an idea with a prototype

## A possible approach...

Project manager

#### ...Our vision!

- 1 Motivation

- 2 Methodology

- Results and Conclusions

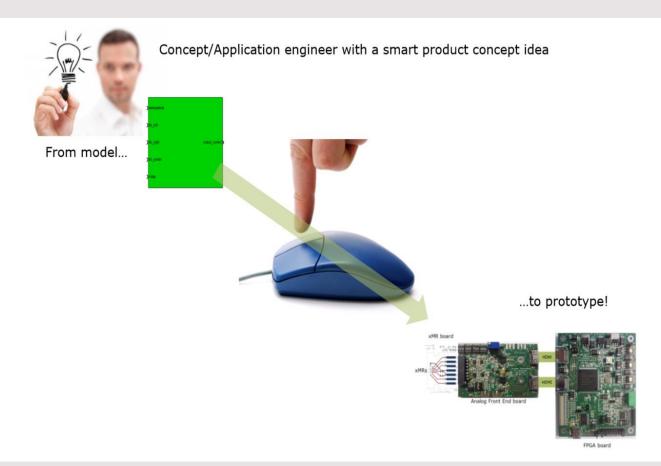

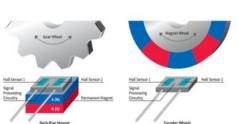

#### Magnetic sensors for automotive applications

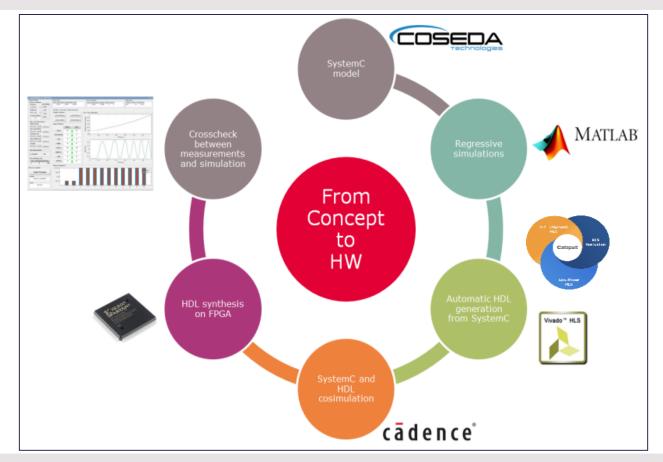

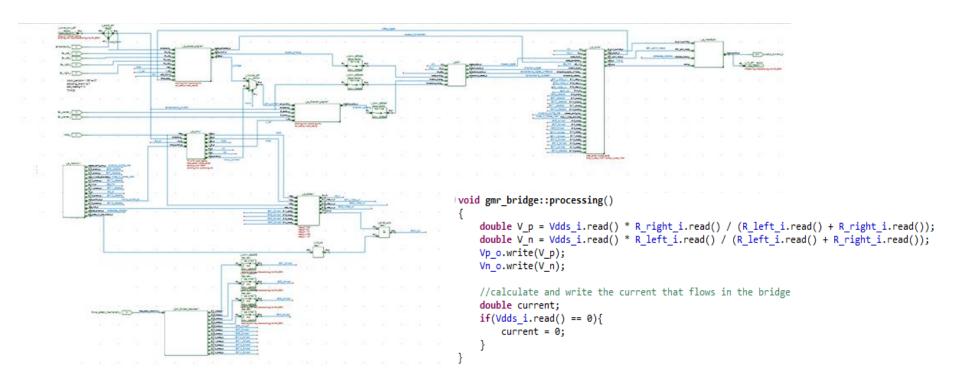

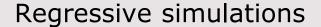

#### Virtual prototyping for concept definition

#### From simulation to real HW

#### Fast & Furious: the methodology in a nutshell

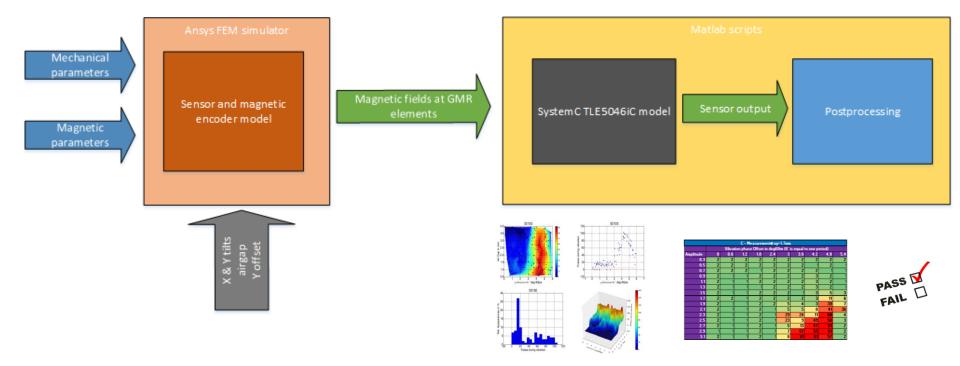

## Coside clean netlist generation 1/3

#### Coside clean netlist generation 2/3

```

€ test sch old.cpp 🛭

h test sch.h ♡

3⊕ // @copyright COSEDA Technologies GmbH. All rights reserved.□

3⊕ // @copyright COSEDA Technologies GmbH. All rights reserved.□

20@ /** ======== DO NOT EDIT THIS FILE! ==========

19 #pragma once

21 * = This file was automatically generated from an COSIDE schematic.

22 * = (recreate via: "test sch.scaml")

21@ /** ========= DO NOT EDIT THIS FILE! ===========

* = This file was automatically generated from an COSIDE schematic.

24 */

* = (recreate via: "test sch.scaml")

25 // include submodules

26 #include <sca basic libraries/arithmetic sc/add2 sc.h>

25

27 #ifndef TEST TEST LIB TEST SCH H

28 // if this file is not included by the header keep implementation

27 #include <systemc>

29 #include "test sch.h"

30 #define COSIDE INCLUDE IMPLEMENTATION

29 /// include submodules

30 #include "sca basic libraries/arithmetic sc/add2 sc.h"

32 // adds SystemC namespaces for user convenience

32@ SC MODULE(test sch)

33 #include <systemc.h>

34 #include <systemc-ams.h>

33 {

34

/// ports

36 // explicitly use std::abs() in any cases

sc core::sc in<short > sc0 i:

37 #include <cmath>

sc core::sc in<short > scl i;

38 using std::abs;

sc core::sc out<short > sc o;

38

39

40⊖ namespace test namespace

/// constructor

40

42 // component declarations

test sch::test sch(sc core::sc module name) :

43@ struct test sch::components

sc0 i("sc0 i"),

sc1 i("sc1 i"),

45

// declare instance references for external access

sc o("sc o"),

add2 sc<short>& i add2 sc1:

i add2 sc1("i add2 sc1")

// declare node and signal references for external access

// component constructor

/// SystemC adder

components (

i add2 sc1.sc0 i(sc0 i);

/** first summand */

50

add2 sc<short>* i add2 sc1

i add2 scl.scl i(scl i):

/** second summand */

51

i add2 scl.sc o(sc o);

/** SUM */

52

i add2 sc1(*i add2 sc1)

53

54

// component destructor

55⊝

~components()

private:

56

Old netlist

New netlist

57

// delete instances

/// parameters

58

delete &i add2 sc1;

58

59

// delete signals

/// signals

59

60

61 };

/// submodule instances

/** SystemC adder */

62 #ifdef COSIDE INCLUDE IMPLEMENTATION

add2 sc<short> i add2 sc1;

62 }:

65 // architecture implementation (netlist)

68@ void test sch::architecture()

69 {

```

#### Coside clean netlist generation 3/3

```

689 void test sch::architecture()

3⊕ // @copyright COSEDA Technologies GmbH. All rights reserved.

19 #pragma once

// generate nodes/signals - map to references and name

21@ /** ======== DO NOT EDIT THIS FILE! ==========

73

* = This file was automatically generated from an COSIDE schematic.

74

* = (recreate via: "test sch.scaml")

// instantiate modules, assign parameter

77

add2 sc<short>::params p i add2 sc1;

78

add2 sc<short> *i add2 sc1:

27 #include <systemc>

79

i add2 sc1 = new add2 sc<short>("i add2 sc1", p i add2 sc1);

29 /// include submodules

// port binding see netlist section

81

#include "sca basic libraries/arithmetic sc/add2 sc.h"

// netlist section

SC_MODULE(test sch)

/// ports

sc core::sc in<short > sc0 i;

sc core::sc in<short > scl i:

Clean netlist

sc core::sc out<short > sc o;

/// constructor

No pointers or complex structures

test sch::test sch(sc core::sc module name) :

sc0 i("sc0 i"),

sc1 i("sc1 i").

sc o("sc o"),

i add2 sc1("i add2 sc1")

96 // constructor/destructor section

/// SystemC adder

98 /// constructor implementation

99@ test_sch::test_sch(sc core::sc module name, const params& pa) :

i add2 scl.sc0 i(sc0 i);

/** first summand */

/** second summand */

// naming ports for debugging

i add2 scl.scl i(scl i);

sc0 i("sc0 i"),

i add2 scl.sc o(sc o);

/** sum */

101

102

sc1 i("sc1 i").

103

sc o("sc o").

104

p(pa)

105 {

private:

106

architecture():

Old netlist

New netlist

107 }

/// parameters

108 /// destructor implementation

/// signals

109@ test_sch::~test_sch()

110 {

111

/// submodule instances

// delete component structure

/** SystemC adder */

112

delete c;

add2 sc<short> i add2 sc1:

113 }

114 #endif // #ifdef COSIDE INCLUDE IMPLEMENTATION

116 } // end namespace test namespace

117

118 // remove temporary defines

119 #undef DONT INCLUDE HIERARCHIC COMPONENTS

120 #undef COSIDE INCLUDE IMPLEMENTATION

```

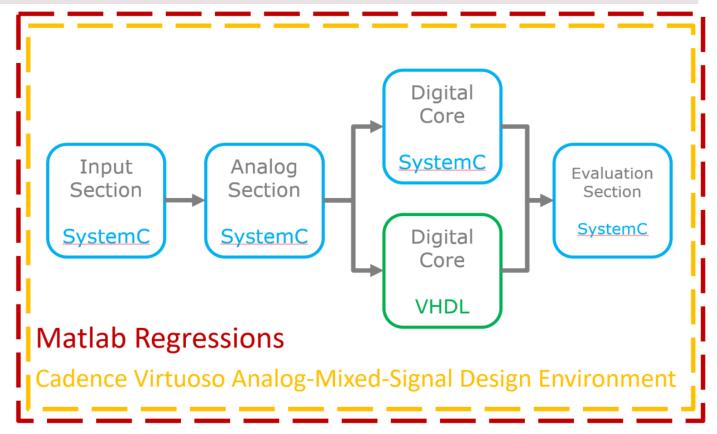

#### From SystemC to HDL in a few clicks

- SystemC "clean" netlist from COSIDE®

- Conversion of each SystemC module

- Conversion of top-level

- High level synthesis

- Vivado HLS

- Mentor Catapult

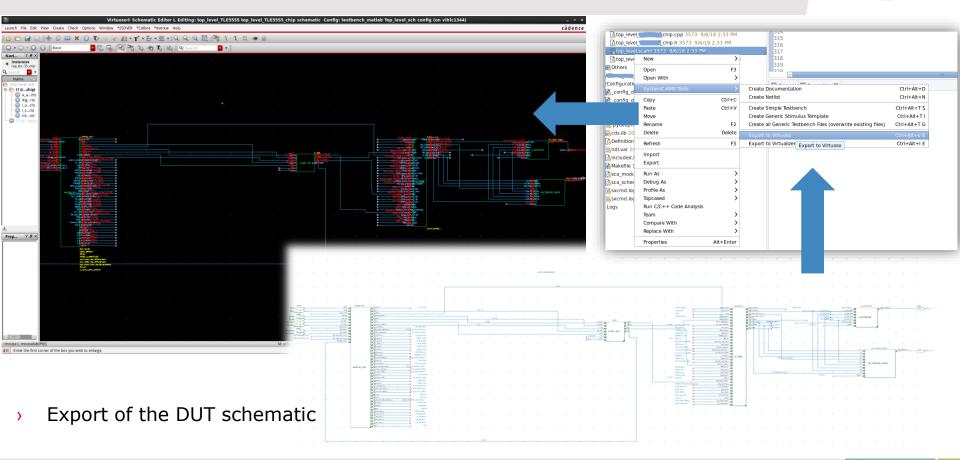

#### Coside CCB - SystemC to Virtuoso Export 1/3

#### Coside CCB - SystemC to Virtuoso Export 2/3

#### Coside CCB – SystemC to Virtuoso Export 3/3

Same netlists ...

#### Coside CCB – SystemC to Virtuoso Export 3/3

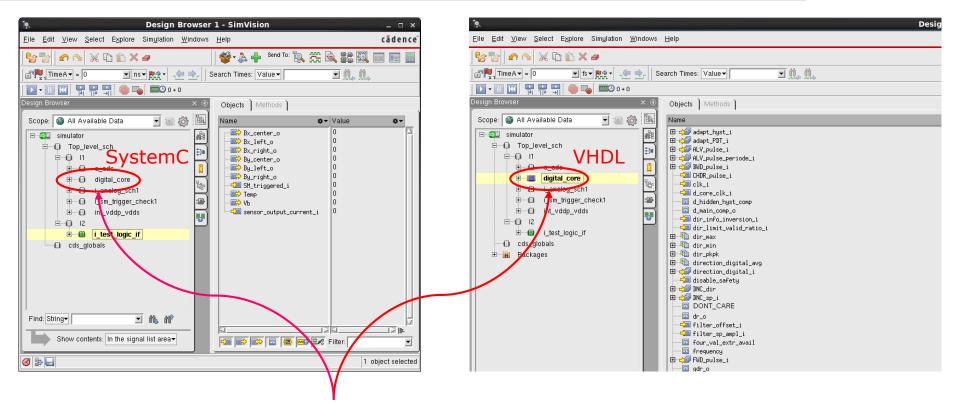

... But different digital cores instances

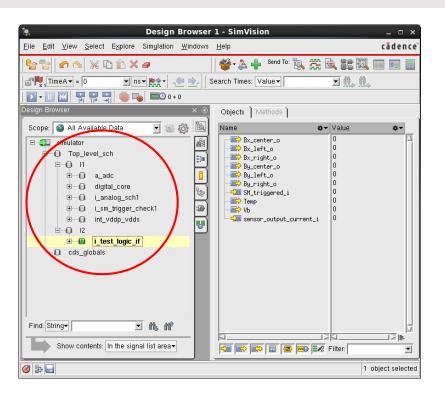

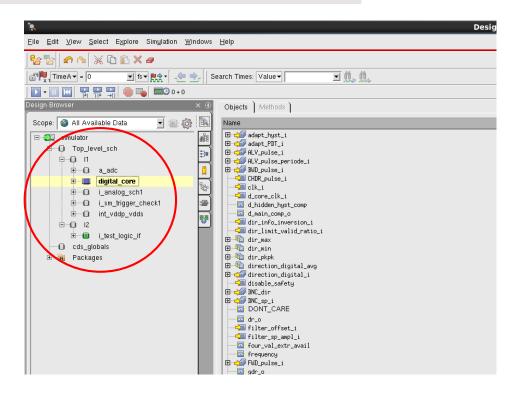

### SystemC & VHDL cosimulation (1/2)

<sup>\*</sup>Note: Mentor Catapult would also allow cosimulation in an integrated environment

2018-10-26

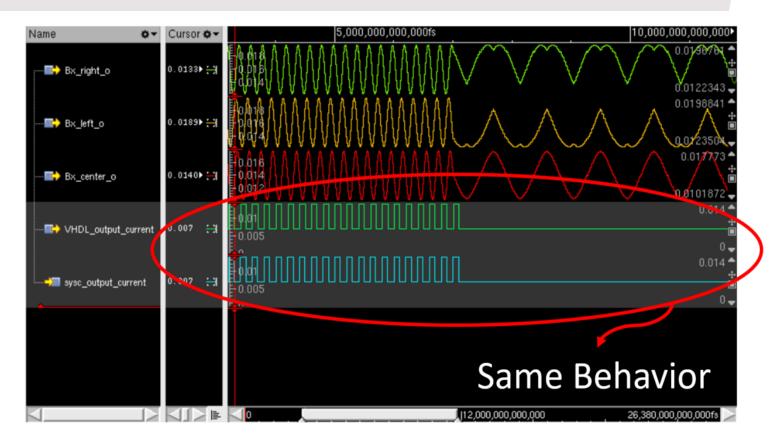

#### SystemC & VHDL cosimulation (2/2)

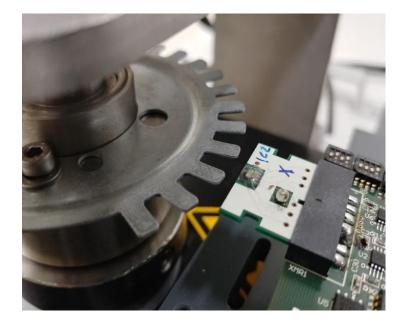

#### Moving to real HW

## **Direction Signal Path**

Analog Front End board

## Speed Signal Path

## Digital core

FPGA board

## Measurements setup in the laboratory

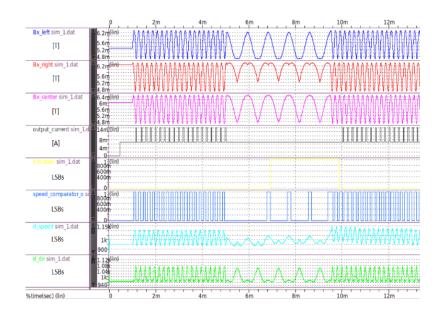

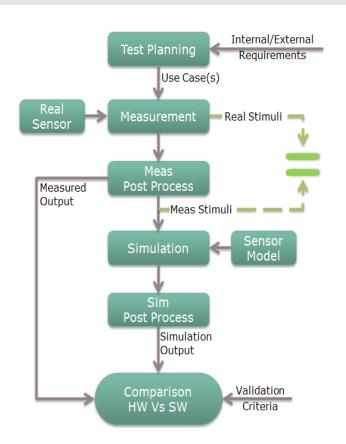

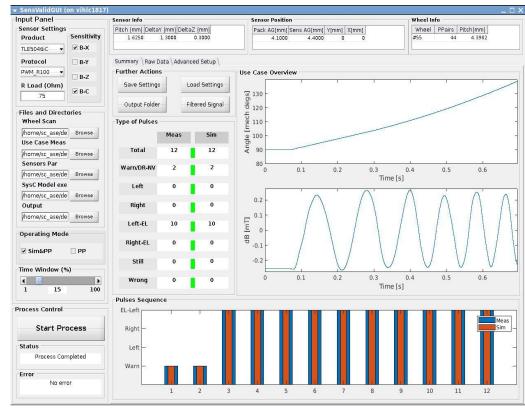

#### Automatic measurement & simulations crosscheck

- 1 Motivation

- 2 Methodology

- Results and Conclusions

How much effort was spent for the different steps in the flow?

- Modeling: 1 month if concept available (SysC reuse) / up to 1 year if concept has to be developed

- Simulation setup: straightforward, just the parameter sweeps and their steps have to be defined

- SysC to HDL conversion: achieved with a one-click approach using Mentor Catapult software

- SysC & HDL cosimulation: made possible by Coseda-Cadence-Bridge (CCB) with one click export

- Synthesis on FPGA possible without any need of modifications, using Xilinx ISE synthesizer

#### Results and Conclusion (2/3)

- How much time was saved by this methodology?

- From virtual to real HW prototype: 3 to 6 man / months faster!

- What is the simulation speed of SysC vs. Matlab vs. SysC/HDL co-sim?

- SystemC: 1ms of simulation → ca. 5 s in the real world

- Matlab: does not affect the simulation speed, only used to handle the regression

- SystemC / HDL co-simulation: around 6 times slower than SystemC due to RTL simulation time (dominant)

#### Results and Conclusion (3/3)

- One-click conversion finally possible

- > HDL and SystemC match 1:1 in cosimulation

- Measurements ongoing, correct functionality already observed

- High level synthesis approach

- Saves development resources and time

- Increase reuse and speed

- Rapid prototyping approach

- Increase design confidence

- Allow better customers interaction

## Questions & Answers

Any questions?

Part of your life. Part of tomorrow.