### You Choose the Way.

We Make the Most of it.

# Analysis of safety and real time behavior using cycle accurate ARM models

#### Agenda

- 1 Objective

- 2 Motivation

- 3 Why cycle accurate models

- 4 Platform setup

- 5 Block diagram

- 6 COSIDE® support

- 7 Outcome

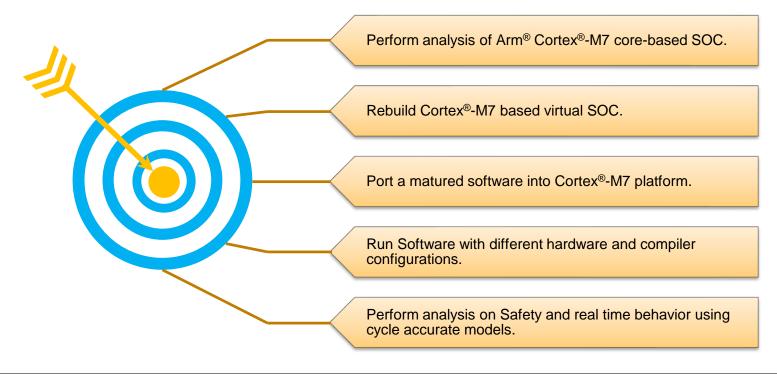

#### **Objective**

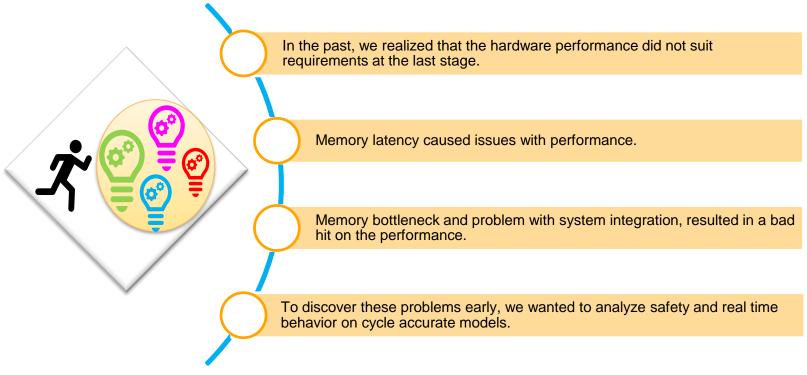

#### **Motivation**

#### Why cycle accurate models

As a part of safety requirement, we have some timing requirements that are too stringent.

To study how quick the code would execute if it is configured in either TCM or memory.

To measure and check the hardware requirements using software and identify where exactly we need higher accuracy.

We wanted to transfer huge data from traffic generator to the core and measure the time consumed.

Public

In fast models, we cannot validate these kind of scenarios and there are high chances that we might get FALSE PASS.

#### **Platform Setup**

#### **Platform Configuration:**

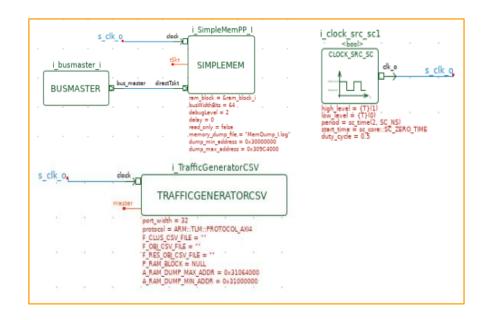

❖ Core: Arm® Cortex®-M7

❖ SystemC models : Cycle accurate models from Arm<sup>®</sup>

Interconnect : NIC 400

❖ SRAM : BP140

Traffic Generator : Conti specific

TCM: Both ITCM and DTCM are used

Cache: Both Instruction and Data Cache are used

Floating point : Single precision floating point

**Memory Map:**

| Address  | Module              | Remarks           |

|----------|---------------------|-------------------|

| 0        | I TCM (private)     | Exception vectors |

| 20000000 | D TCM (private)     | Stack and heap    |

| 30000000 | Global RAM0 (BP140) | Application code  |

| 31000000 | Global RAM1 (BP140) | Application Data  |

#### Tool chain:

❖ IDE used : COSIDE® 2.7 RC

Compiler : GNU Arm Embedded Toolchain

**Business Unit ADAS / IC Solutions**

**Public**

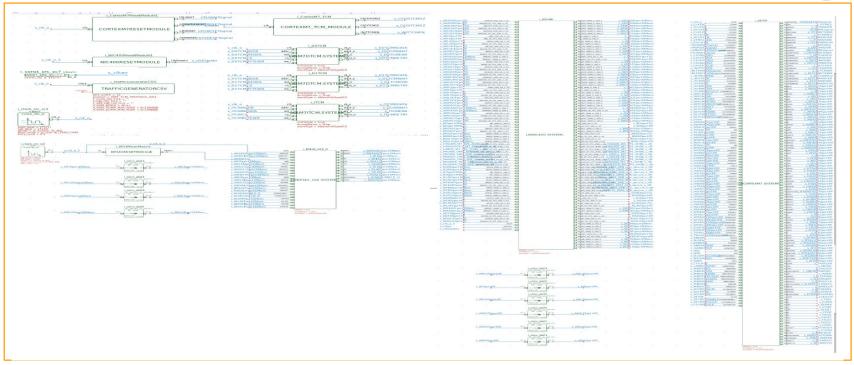

## **Block diagram**

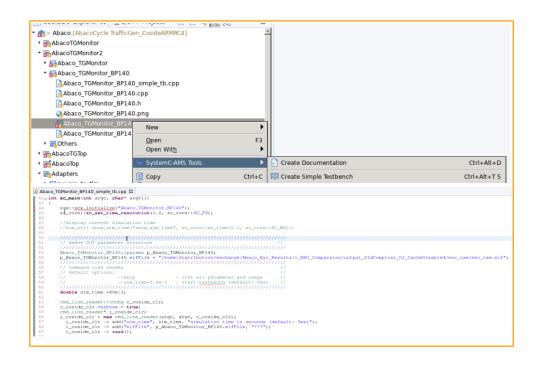

#### **COSIDE®** support

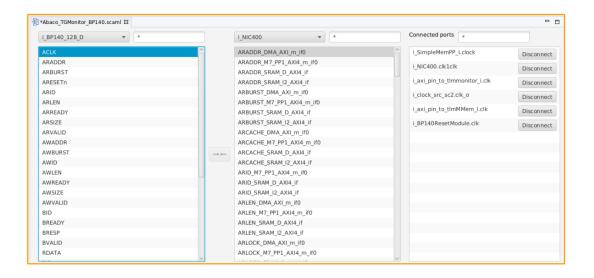

Most of the models were pin level models. So we had to do several connections, re-integrations when we receive the updated models. Interface definitions and wiring editor feature helped us overcome the connection issues.

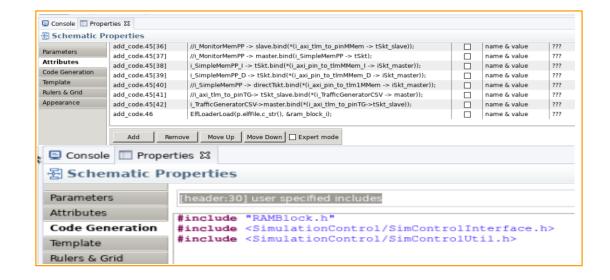

We were able to generate the manual code in few places by using the 'attributes' and 'code generation' feature. Using this feature, we were able to successfully bind few TLM ports.

**Business Unit ADAS / IC Solutions**

Public

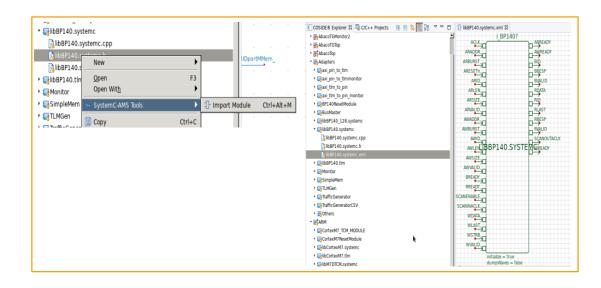

With many basic options that are provided, we were able to import models from Arm®, create custom models, integrate all of those and create our custom SOC platform.

Automatic generation of models(xml and symbols) from the header files, i.e. SystemC projects were automatically created from the header files provided by Arm<sup>®</sup>.

Templated module and parameters support the configuration of models with different bus width, protocol selection, width, different clock port configurations, start and end address of memory, VCD generation control, log file generations etc.

Public

Automatic test bench generation with support of parameters lead to run various software without rebuilding the platform.

14

#### **Outcome**

✓ Analyzed whether Arm® Cortex®-M7 features fit our needs.

✓ Observed the behavior of software at various memory speeds and different hardware configuration.

✓ Studied behavior of software with different compilers, various compiler and linker options.

✓ Approximately 50KB of data is transferred between Core, RAM and Traffic generator for every few ms and we got the expected response out of it.

✓ Compared the results with the hardware implementation.

Thank you for your attention!